investigacion 6

DRAM

DRAM(Dynamic Random Access Memory) es un tipo de memoria dinamica de acceso aleatorio que se usa principalmente en los módulos de memoria RAM y en otros dispositivos, como memoria principal del sistema. Se denomina dinámica, ya que para mantener almacenado un dato, se requiere revisar el mismo y recargarlo, cada cierto período, en un ciclo de refresco. Su principal ventaja es la posibilidad de construir memorias con una gran densidad de posiciones y que todavía funcionen a una velocidad alta: en la actualidad se fabrican integrados con millones de posiciones y velocidades de acceso medidos en millones de bit por segundo. Es una memoria volátil, es decir cuando no hay alimentación eléctrica, la memoria no guarda la información. Inventada a finales de los sesenta, es una de las memorias más usadas en la actualidad

Reinvención de la memoria DRAMPara 1973 Intel y otros fabricantes construían y empacaban sus integrados de memoria DRAM empleando un esquema en el que se aumentaba un pin por cada vez que se doblaba la capacidad. De acuerdo a este esquema, un integrado de 64 kilobits tendría 16 pines solo para las direcciones. Dentro de los costos más importantes para el fabricante y el ensamblador de circuitos impresos estaba la cantidad de pines del empaque y en un mercado tan competido era crucial tener los menores precios. Debido a eso, un integrado con una capacidad de 16 pines y 4Kb de capacidad fue un producto apreciado por los usuarios, que encontraban a los integrados de 22 pines, ofrecidos por Intel y Texas Instruments como insumos costosos.

El lanzamiento de la memoria MK4096 de 4K, con un solo transistor por celda y con direccionamiento multiplexado resultó del trabajo de Robert Proebsting quien observo que en las celdas con un solo transistor, era imposible acceder la información en una posición, enviando al mismo tiempo los datos de fila y columna a la matriz: había que enviar las señales una después de la otra. La solución a nivel de la celda conducía a un ahorro en el empaque, ya que la dirección podría recibirse en dos etapas, reduciendo la cantidad de pines usados.[9] Por ejemplo para un integrado de 64 Kb se pasaba de 16 pines dedicados a solo 8 y dos más para señales de control extra. La multiplexación en tiempo es un esquema de direccionamiento que trae muchas ventajas, a costa de unos pocos cambios en el circuito externo, de manera que se convirtió en un estándar de la industria que todavía se mantiene. Mucha de la terminología usada en la hoja de datos del MK4096 todavía se usa y muchos de los parámetros de temporización como el retardo RAS a CAS fueron instaurados con ese producto, entre otros aspectos.[10]

Funcionamiento

La celda de memoria es la unidad básica de cualquier memoria, capaz de almacenar un Bit en los sistemas digitales. La construcción de la celda define el funcionamiento de la misma, en el caso de la DRAM moderna, consiste en un transistor de efecto de campo y un condensador. El principio de funcionamiento básico, es sencillo: una carga se almacena en el condensador significando un 1 y sin carga un 0. El transistor funciona como un interruptor que conecta y desconecta al condensador. Este mecanismo puede implementarse con dispositivos discretos y de hecho muchas memorias anteriores a la época de los semiconductores, se basaban en arreglos de celdas transistor-condensador.

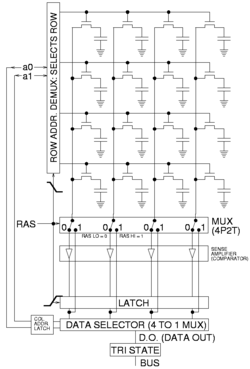

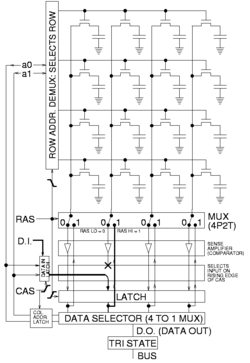

Las celdas en cualquier sistema de memoria, se organizan en la forma de matrices de dos dimensiones, a las cuales se accede por medio de las filas y las columnas. En la DRAM estas estructuras contienen millones de celdas y se fabrican sobre la superficie de la pastilla de silicio formando áreas que son visibles a simple vista. En el ejemplo tenemos un arreglo de 4x4 celdas, en el cual las líneas horizontales conectadas a las compuertas de los transistores son las llamadas filas y las líneas verticales conectadas a los canales de los FET son las columnas.

Para acceder a una posición de memoria se necesita una dirección de 4 bits, pero en las DRAM las direcciones están multiplexadas en tiempo, es decir se envían por mitades. Las entradas marcadas como a0 y a1 son el bus de direcciones y por el mismo entra la dirección de la fila y después la de la columna. Las direcciones se diferencian por medio de señales de sincronización llamadas RAS (del inglés Row Address Strobe) y CAS (Column Address Strobe) que indican la entrada de cada parte de la dirección.

Los pasos principales para una lectura son:

- Las columnas son precargadas a un voltaje igual a la mitad del voltaje de 1 lógico. Esto es posible ya que las líneas se comportan como grandes condensadores, dada su longitud tienen un valor más alto que la de los condensadores en las celdas.

- Una fila es energizada por medio del decodificador de filas que recibe la dirección y la señal de RAS. Esto hace que los transistores conectados a una fila conduzcan y permitiendo la conexión electrica entre las líneas de columna y una fila de condensadores. El efecto es el mismo que se produce al conectar dos condensadores, uno cargado y otro de carga desconocida: se produce un balance de que deja a los dos con un voltaje muy similar, compartiendo las cargas. El resultado final depende del valor de carga en el condensador de la celda conectada a cada columna. El cambio es pequeño, ya que la línea de columna es un condensador más grande que el de la celda.

- El cambio es medido y amplificado por una sección que contiene circuitos de realimentación positiva: si el valor a medir es menor que el la mitad del voltaje de 1 lógico, la salida será un 0, si es mayor, la salida se regenera a un 1. Funciona como un redondeo.

- La lectura se realiza en todas las posiciones de una fila de manera que al llegar la segunda parte de la dirección, se decide cual es la celda deseada. Esto sucede con la señal CAS. El dato es entregado al bus de datos por medio de la lineo D.O. y las celdas involucradas en el proceso son reescritas, ya que la lectura de la DRAM es destructiva.

La escritura en una posición de memoria tiene un proceso similar al de arriba, pero en lugar de leer el valor, la línea de columna es llevada a un valor indicado por la línea D.I. y el condensador es cargado o descargado. El flujo del dato es mostrado con una línea gruesa en el gráfico

SRAM

Static Random Access Memory (SRAM), o Memoria Estática de Acceso Aleatorio es un tipo de memoria basada en semiconductores que, a diferencia de la memoria DRAM, es capaz de mantener los datos (mientras esté alimentada) sin necesidad de circuito de refresco (no se descargan). Sin embargo, sí son memorias volátiles, es decir que pierden la información si se les interrumpe la alimentación eléctrica.

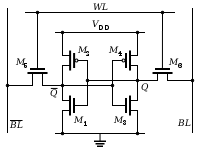

DiseñoEstas memorias son de Acceso Aleatorio, lo que significa que las posiciones en la memoria pueden ser escritas o leídas en cualquier orden, independientemente de cual fuera la última posición de memoria leída o escrita. Cada bit en una SRAM se almacena en cuatro transistores, que forman un biestable. Este biestable tendrá dos estados, utilizados para almacenar un 0 o un 1. Se utilizan otros dos transistores adicionales para controlar el acceso al biestable durante las operaciones de lectura y escritura. Una SRAM típica utilizará seis MOSFET para almacenar cada bit. Adicionalmente, podemos encontrar otros tipos de SRAM, que utilizan ocho, diez, o más transistores por bit.[1] [2] [3] Esto es utilizado para implementar más de un puerto de lectura o escritura en determinados tipos de memoria de video.

Un menor número de transistores por celda, hará posible reducir el tamaño de esta, reduciendo el coste por bit en la fabricación, al poder implementar más celdas en una misma oblea de silicio.

Es posible fabricar celdas que utilicen menos de seis transistores, pero en los casos de tres transistores[4] [5] o un solo transistor estaríamos hablando de memoria DRAM, no SRAM.

El acceso a la celda es controlado por un bus de control (WL en la figura), que controla los dos transistores de acceso M5 y M6, quienes controlan si la celda debe ser conectada a los buses BL y BL. Ambos son utilizados para transmitir datos tanto para las operaciones de lectura como las de escritura, y aunque no es estrictamente necesario disponer de abos buses, se suelen implementar para mejorar los margenes de ruido.

A diferencia de la DRAM, en la cual la señal de la línea de salida se conecta a un capacitador, y este es el que hace oscilar la señal durante las operaciones de lectura, en las celdas SRAM son los propios biestables los que hacen oscilar dicha señal, mientras que la estructura simétrica permite detectar pequeñas variaciones de voltaje con mayor precisión. Otra ventaja de las memorias SRAM frente a DRAM, es que aceptan recibir todos los bits de dirección al mismo tiempo.

El tamaño de una memoria SRAM con m líneas de dirección, y n líneas de datos es 2m palabras, o 2m × n bits. Modos de operación de una SRAM

Una memoria SRAM tiene tres estados distintos de operación: standby, en el cual el circuito está en reposo, reading o lectura, durante el cual los datos son leídos desde la memoria, y writing o escritura, durante el cual se actualizan los datos almacenados en la memoria.

Reposo

Si bus de control (WL) no está activado, los transistores de acceso M5 y M6 desconectan la celda de los buses de datos. Los dos biestables formados por M1 – M4 mantendrán los datos almacenados mientras dure la alimentación electrica.

Lectura

Asumimos que el contenido de la memoria es 1, y está almacenado en Q. El ciclo de lectura comienza cargando los buses de datos con el 1 lógico, y luego activa WL y los transistores de control. A continuación, los valores almacenados en Q y Q se transfieren a los buses de datos, dejando BL en su valor previo, y ajustando BL a través de M1 y M5 al 0 lógico. En el caso que el dato contenido en la memoria fuera 0, se produce el efecto contrario: BL será ajustado a 1 y BL a 0.

Escritura

El ciclo de escritura se inicia aplicando el valor a escribir en el bus de datos. Si queremos escribir un 0, ajustaremos BL a 1 y BL a 0, mientras que para un 1, basta con invertir los valores de los buses. Una vez hecho esto, se activa el bus WL, y el dato queda almacenado.

Aplicaciones y Usos

edCaracterísticas

La memoria SRAM es más cara, pero más rápida y con un menor consumo (especialmente en reposo) que la memoria DRAM. Es utilizada, por tanto, cuando es necesario disponer de un mejor tiempo de acceso, o un consumo reducido, o ambos. Debido a su compleja estructura interna, es menos densa que DRAM, y por lo tanto no es utilizada cuando es necesaria una alta capacidad de datos, como por ejemplo en la memoria principal de los ordenadores personales.

[ Frecuencia de reloj y potencia

El consumo electrico de una SRAM varía dependiendo de la frencuencia con la cual se accede a la misma: puede llegar a tener un consumo similar a DRAM cuando es usada en alta frecuencia, y algunos circuitos integrados pueden consumir varios vatios durante su funcionamiento. Por otra parte, las SRAM utilizadas con una frecuencia baja, tienen un consumo muy bajo, del orden de micro-vatios.

Usos de las SRAM

- como producto de propósito general:

- con interfaces asíncronas como chips 32Kx8 de 28 pines (nombrados XXC256), y productos similares que ofrecen transferencias de hasta 16Mbit por chip.

- con interfaces síncronas, principalmente como caches y otras aplicaciones que requieran transferencias rápidas, de hasta 18Mbit por chip.

- integrados en chip:

TONTHOS

Usos integrados en productos

Las SRAM se utilizan en sistemas científicos e industriales, electrónica del automóvil, y similares. También se pueden encontrar en prácticamente todos los productos de uso cotidiano que implementen una interfaz electrónica de usuario.

También podemos encontrar memorias SRAM en los ordenadores personales, estaciones de trabajo, routers y la totalidad de periféricos de los mismos.

Uso de aficionados

Los aficionados a la electrónica prefieren las memorias SRAM debido a su sencilla interfaz, ya que es mucho más fácil trabajar con SRAM que con DRAM, al no existir ciclos de refresco, y poder acceder directamente a los buses de dirección y de datos en lugar de tener que utilizar multiplexores. Además, las SRAM solo necesitan tres buses de control: Chip Enable (CE), Write Enable (WE), y Output Enable (OE). En el caso de las SRAM síncronas, tendremos además la señal de reloj (CLK)

Tipos de SRAM

SRAM no volátiles

Las memorias SRAM no volátiles (NVRAM) presentan el funcionamiento típico de las RAM, pero con la característica distintiva de que los datos almacenados en ellas son preservados aun cuando se interrumpe la alimentación eléctrica. Se utilizan en situaciones donde se requiere conservar la información almacenada sin necesidad de alimentación alguna para ello; normalmente donde se desea evitar el uso de baterías (o bien no es posible

SDRAM

Synchronous Dynamic Random Access Memory (SDRAM) es una memoria dinámica de acceso aleatorio DRAM que tiene una interfaz síncrona. Tradicionalmente, la memoria dinámica de acceso aleatorio DRAM tiene una interfaz asíncrona, lo que significa que el cambio de estado de la memoria tarda un cierto tiempo, dado por las características de la memoria, desde que cambian sus entradas. En cambio, en las SDRAM el cambio de estado tiene lugar en el momento señalado por una señal de reloj y, por lo tanto, está sincronizada con el bus de sistema del ordenador. El reloj también permite controlar una máquina de estados finitos interna que controla la función de "pipeline" Segmentación (informática)|segmentación de las instrucciones de entrada. Esto permite que el chip tenga un patrón de operación más complejo que la DRAM asíncrona, que no tiene una interfaz de sincronización.

El método de segmentación significa que el chip puede aceptar una nueva instrucción antes de que haya terminado de procesar la anterior. En una escritura de datos, el comando "escribir" puede ser seguido inmediatamente por otra instrucción, sin esperar a que los datos se escriban en la matriz de memoria. En una lectura, los datos solicitados aparecen después de un número fijo de pulsos de reloj tras la instrucción de lectura, durante los cuales se pueden enviar otras instrucciones adicionales. (Este retraso se llama latencia y es un parámetro importante a considerar cuando se compra una memoria SDRAM para un ordenador.)

Las SDRAM son ampliamente utilizadas en los ordenadores, desde la original SDRAM y las posteriores DDR SDRAM|DDR (o DDR1), DDR2 y DDR3. Actualmente se está diseñando la DDR4 y se prevé que estará disponible en 2012

Calendario SDRAM

Existen varios límites en el desempeño de DRAM. Más conocido es el tiempo de ciclo de lectura, el tiempo entre las sucesivas operaciones de lectura a una fila abierta. Esta vez se redujo de 10 ns a 100 MHz SDRAM de 5 ns para DDR-400, pero se ha mantenido relativamente sin cambios a través de DDR2-800 y DDR3-1600 generaciones. Sin embargo, al operar los circuitos de interfaz en múltiplos cada vez mayor de la tasa de lectura fundamental, el ancho de banda alcanzable ha aumentado rápidamente.

Otro límite es la latencia CAS, el tiempo entre el suministro de una dirección de la columna y la recepción de los datos correspondientes. De nuevo, esto se ha mantenido relativamente constante a través de 10-15 ns las últimas generaciones de DDR SDRAM.

En la operación, la latencia CAS es un número específico de ciclos de reloj programado en el modo de registro de la SDRAM y espera por el controlador de memoria DRAM. Cualquier valor puede ser programado, pero la SDRAM no funcionará correctamente si es demasiado bajo. A mayores tasas de reloj, la latencia CAS útil en ciclos de reloj, naturalmente, aumenta. 10-15 ns es de 2-3 ciclos (CL2-3) de reloj de 200 MHz de DDR-400 SDRAM, CL4-6 para DDR2-800, y CL8-12 para DDR3-1600. Más lenta de ciclos de reloj, naturalmente, permitirá a los números más bajos de los ciclos de latencia de CAS.

Módulos SDRAM tienen sus propias especificaciones de tiempo, que puede ser más lento que los de los chips en el módulo. Cuando los chips SDRAM de 100 MHz aparecieron por primera vez, algunos fabricantes venden "de 100 MHz" módulos que no podrían funcionar de forma fiable en esa frecuencia de reloj. En respuesta, Intel publicó el estándar PC100, que describe los requisitos y directrices para la producción de un módulo de memoria que puede funcionar de forma fiable a 100 MHz. Esta norma fue muy influyente, y el término "PC100" rápidamente se convirtió en un identificador común para módulos SDRAM de 100 MHz, y los módulos son ahora comúnmente designada con "PC"-números de prefijo (PC66, PC100 o PC133 - aunque el significado real de los números ha cambiado).

SDR SDRAM

Originalmente conocido simplemente como SDRAM, SDRAM tipo de datos solo puede aceptar un comando y la transferencia de una palabra de datos por ciclo de reloj. Las frecuencias de reloj típicas son 100 y 133 MHz. Chips están hechos con una variedad de tamaños de bus de datos (el más común 4, 8 ó 16 bits), pero los chips son generalmente montados en módulos DIMMs de 168-pines que leen o escriben 64 (non-ECC) o 72 (ECC) de bits a la vez.

El uso del bus de datos es complejo y requiere un controlador de memoria DRAM complejo. Esto es porque los datos escritos en la memoria DRAM deben ser presentadas en el mismo ciclo que escribir un comando, pero lee producir una salida de 2 o 3 ciclos después de que el comando de lectura. El controlador de memoria DRAM debe asegurarse de que el bus de datos nunca se requiere de una escritura y lectura, al mismo tiempo.

Típico SDRAM SDR velocidades de reloj de 66, 100 y 133 MHz (períodos de 15, 10, y el 7,5 ns). Frecuencias de reloj de hasta 150 MHz estaban disponibles para los entusiastas del rendimiento.

Las señales de control de SDRAM

Todos los comandos están programados en relación con el flanco de subida de una señal de reloj. Además del reloj, hay 6 señales de control, en su mayoría de baja activa, que se muestra en el flanco de subida del reloj:

- Reloj ‘’’CKE’’’ Habilitar. Cuando esta señal es baja, el chip se comporta como si el reloj se ha detenido. No comandos son interpretados y tiempos de latencia de comando no transcurrir. El estado de las líneas de control de otros no es relevante. El efecto de esta señal es en realidad un retraso de un ciclo de reloj. Es decir, el producto actual ciclo de reloj, como de costumbre, pero el siguiente ciclo de reloj es ignorado, excepto para la prueba de nuevo la entrada de CKE. Reanudar las operaciones normales en el flanco de subida del reloj después de aquel en el que se toman muestras de CKE alta.

Dicho de otra manera, todas las operaciones de microprocesadores también se programan en relación con el flanco ascendente de un reloj de enmascarados. El reloj enmascarado es el lógico de la entrada de reloj y el estado de la señal de CKE en el flanco de subida anterior de la entrada de reloj.

- ‘’’/ CS’’’ Chip Select. Cuando esta señal es alta, el chip hace caso omiso de todas las otras entradas (excepto para CKE), y actúa como si se recibe un comando NOP.

- ‘’’DQM’’’ ocultar los datos. (La letra Q aparece porque, siguiendo las convenciones de la lógica digital, las líneas de datos se conoce como "DQ" líneas.) Al alta, estas señales de supresión de los datos I / O. Cuando acompañan a escribir los datos, los datos no son en realidad por escrito a la DRAM. Cuando afirmó alta dos ciclos antes de un ciclo de lectura, la lectura de datos no es la salida del chip. Hay una línea DQM por 8 bits en un chip x16 de memoria o DIMM.

- ‘’’/RAS’’’ fila Dirección Strobe. A pesar del nombre, este no es un estrobo, sino simplemente un poco de comandos. Junto con / CAS y / WE, esto selecciona uno de los 8 comandos.

- ‘’’/ CAS’’’ columna Dirección Strobe. A pesar del nombre, este no es un estrobo, sino simplemente un poco de comandos. Junto con / RAS y / WE, esto selecciona uno de los 8 comandos.

- ‘’’/ WE’’’ modo escritura. Junto con / RAS y CAS, esta selecciona uno de los 8 comandos. Esto generalmente se distingue de lectura como los comandos de escribir-como comandos.

Dispositivos SDRAM se dividen internamente en 2 o 4 bancos de datos interna independiente. Uno o dos entradas de la dirección del banco (BA0 y BA1) seleccionar un comando de que el banco se dirige.

Muchos de los comandos también utilizar una dirección presentados en los pines de dirección de entrada. Algunos comandos, que o bien no utilizar una dirección, o presentar una columna de dirección, también utilizan A10 para seleccionar variantes. Los comandos de entender son los siguientes.

| /CS | /RAS | /CAS | /WE | BAn | A10 | An | Comandos |

|---|---|---|---|---|---|---|---|

| H | x | x | x | x | x | x | Comando do inhibir (No operación) |

| L | H | H | H | x | x | x | Ninguna operación |

| L | H | H | L | x | x | x | Burst Terminar: Parada de una ráfaga de lectura o escritura en el progreso estallido. |

| L | H | L | H | banco | L | columna | Leer: Leer una ráfaga de datos de la fila activa. |

| L | H | L | H | banco | H | columna | Lea con precarga automática: Como el anterior, y precarga (fila cerca) cuando termine. |

| L | H | L | L | banco | L | columna | Escribe: Escribe una ráfaga de datos a la fila activa. |

| L | H | L | L | banco | H | columna | Escribir con precarga automática: Como el anterior, y precarga (fila cerca) cuando termine. |

| L | L | H | H | banco | row | Active (Activar): abrir una línea de comandos Leer y Escribir | |

| L | L | H | L | banco | L | x | Precarga: Desactivar la fila actual del banco seleccionado. |

| L | L | H | L | x | H | x | Precargar todos: Desactivar la fila actual de todos los bancos. |

| L | L | L | H | x | x | x | Actualización automática: Actualizar una fila de cada banco, utilizando un contador interno. Todos los bancos deben ser precargado. |

| L | L | L | L | 0 0 | mode | Registro de modo de carga: A0 a través de A9 se cargan para configurar el chip DRAM Los ajustes más importantes son la latencia CAS (2 o 3 ciclos) y la longitud de la ráfaga (1, 2, 4 u 8 ciclos | |

De datos único SDRAM tiene una tasa de 10 páginas a un bit de modo de registro programable. Más tarde, el doble de datos de normas de SDRAM tasa añadir registros modo adicional, se dirigió a utilizar los pines banco de direcciones. Para SDRAM SDR, las clavijas de Dirección del Banco y las líneas de dirección A10 y encima se pasan por alto, pero debe ser cero durante un registro de modo de escribir.

Los bits se M9 a través de M0, presentado por la A9 a través de líneas de dirección A0 durante un ciclo de carga de registro de modo.

- M9: Escribe el modo ráfaga. Si es 0, escribe utilizar la longitud de la ráfaga y el modo de leer. Si 1, todas las escrituras no son de estallido (ubicación única).

- M8, M7: modo de funcionamiento. Reservado, y debe ser 00.

- M6, M5, M4: latencia CAS. En general, sólo 010 (CL2) y 011 (CL3) son legales. Especifica el número de ciclos entre un comando de lectura y de salida de datos del chip. El chip tiene un límite fundamental de este valor en nanosegundos, durante la inicialización, el controlador de memoria debe utilizar su conocimiento de la frecuencia de reloj de traducir ese límite en los ciclos.

- M3: Tipo de ráfaga. 0 - peticiones estallido secuencial de pedidos, mientras que 1 peticiones intercalados estallido de pedido.

- M2, M1, M0: longitud de la ráfaga. Los valores de 000, 001, 010 y 011 especifican un tamaño de ráfaga de 1, 2, 4 u 8 palabras, respectivamente. Cada leer (y escribir, si M9 es 0) llevará a cabo que tiene acceso a muchos, a no ser interrumpido por una parada de reventar o otro comando. Un valor de 111 especifica una explosión fila completa. La explosión continuará hasta que se interrumpan. Full estallidos de fila sólo se permite con el tipo de explosión secuencial.

Actualización automática

Es posible cargar un chip de memoria RAM por la apertura y cierre (activación y precarga) cada fila de cada banco. Sin embargo, para simplificar el controlador de memoria, los chips SDRAM de apoyo a una "actualización automática" de comando, que realiza estas operaciones a una fila de cada banco de forma simultánea. La SDRAM también mantiene un contador interno, que itera sobre todos los registros posibles. El controlador de memoria, simplemente debe enviar un número suficiente de comandos de actualización automática (una por fila, 4096 en el ejemplo que hemos estado usando) cada intervalo de actualización (TREF = 64 ms es un valor común). Todos los bancos debe estar inactivo (cerrado, precargado) cuando se emite este comando.

Modos de bajo consumo

Como se mencionó, el reloj de habilitar (CKE) de entrada puede ser usada efectivamente para detener el reloj a una SDRAM. La entrada de CKE se muestra cada flanco de subida del reloj, y si es baja, el siguiente flanco de subida del reloj se omite para cualquier otro fin que el control de CKE.

CKE Si se baja, mientras que la SDRAM está realizando operaciones, sino que simplemente se "congela" en el lugar hasta CKE se eleva de nuevo.

Si la SDRAM está inactiva (todos los bancos precargado, ningún comando en curso), cuando se baja de CKE, la SDRAM entra automáticamente en modo power-down, poder de consumo mínimo hasta CKE se eleva de nuevo. Esto no debe durar más de TREF el máximo intervalo de actualización, o la memoria del contenido se puede perder. Es legal para detener el reloj en su totalidad durante este tiempo para el ahorro de energía adicional.

Por último, si CKE se reduce al mismo tiempo, como un auto de comando de actualización se envía a la SDRAM, SDRAM entra en el modo de auto-actualización. Esto es como el poder hacia abajo, pero la SDRAM utiliza un temporizador en chip interno para generar ciclos de actualización cuando sea necesario. El reloj puede ser detenido durante este tiempo. Si bien el modo de auto-actualización consume un poco más de modo power-down, permite que el controlador de memoria para ser desactivado por completo, lo que comúnmente más que compensa la diferencia.

DIMM

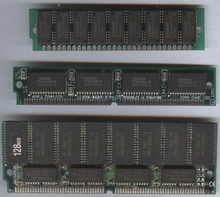

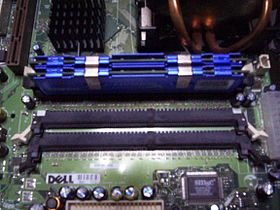

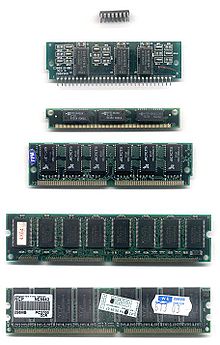

DIMM son las siglas de «Dual In-line Memory Module» y que podemos traducir como Módulo de Memoria en linea doble. Son módulos de memoria RAM utilizados en ordenadores personales. Se trata de un pequeño circuito impreso que contiene chips de memoria y se conecta directamente en ranuras de la placa base. Los módulos DIMM son reconocibles externamente por poseer sus contactos (o pines) separados en ambos lados, a diferencia de los SIMM que poseen los contactos de modo que los de un lado están unidos con los del otro.

Las memorias DIMM comenzaron a reemplazar a las SIMM como el tipo predominante de memoria cuando los microprocesadores Intel Pentium dominaron el mercado.

Un DIMM puede comunicarse con el PC a 64 bits (y algunos a 72 bits) en vez de los 32 bits de los SIMMs.

Funciona a una frecuencia de 133 MHz cada una.

Los módulos en formato DIMM (Módulo de Memoria en Línea Doble),al ser memorias de 64 bits, lo cual explica por qué no necesitan emparejamiento. Los módulos DIMM poseen chips de memoria en ambos lados de la placa de circuito impresa, y poseen a la vez, 84 conectores de cada lado, lo cual suma un total de 168 clavijas. Además de ser de mayores dimensiones que los módulos SIMM (130x25mm), estos módulos poseen una segunda muesca que evita confusiones.

Cabe observar que los conectores DIMM han sido mejorados para facilitar su inserción, gracias a las palancas ubicadas a ambos lados de cada conector.

También existen módulos más pequeños, conocidos como SO DIMM (DIMM de contorno pequeño), diseñados para ordenadores portátiles. Los módulos SO DIMM sólo cuentan con 144 clavijas en el caso de las memorias de 64 bits, y con 77 clavijas en el caso de las memorias de 32 bits.

Especificación de los módulos DIMM- DIMMs de 168 contactos, [DIMM] SDR SDRAM. (Tipos: PC66, PC100, PC133, ...)

- DIMMs de 184 contactos, DDR SDRAM. (Tipos: PC1.600 (DDR-200), PC2.100 (DDR-266), PC2.400 (DDR-300), PC2.700 (DDR-333), PC3.00 (DDR-366), PC3.200 (DDR-400), PC3.500 (DDR-433), PC3.700 (DDR-466), PC4.000 (DDR-500), PC4.300 (DDR-533), PC4.800 (DDR-600) => Hasta 1 GiB/módulo)

- DIMMs de 240 contactos, DDR2 SDRAM. (Tipos: PC2-3.200 (DDR2-400), PC2-3.700 (DDR2-466), PC2-4.200 (DDR2-533), PC2-4.800 (DDR2-600), PC2-5.300 (DDR2-667), PC2-6.400 (DDR2-800), PC2-8.000 (DDR2-1.000), PC2-8.500 (DDR2-1.066), PC2-9.200 (DDR2-1.150) y PC2-9.600 (DDR2-1.200) => Hasta 4 GiB por módulo)

- DIMMs de 240 contactos, DDR3 SDRAM. (Tipos: PC3-6.400 (DDR3-800), PC3-8.500 (DDR3-1.066), PC3-10.600 (DDR3-1.333), PC3-11.000 (DDR3-1.375), PC3-12.800 (DDR3-1.600),PC3-13.000 (DDR3-1.625), PC3-13.300 (DDR3-1.666), PC3-14.400 (DDR3-1.800), PC3-16.000 (DDR3-2.000) => Hasta 4 GiB por módulo)

ETC.

Correción de errores

Los ECC DIMMs son aquellos que tienen un mayor número de bits de datos, los cuales son usados por los controladores del sistema de memoria para detectar y corregir errores. Hay multitud de esquemas ECC, pero quizás el más común es el Corrector de errores individuales-Detector de errores dobles (SECDED) que usa un byte extra por cada palabra de 64 bits. Los módulos ECC están formados normalmente por múltiplos de 9 chips y no de 8 como es lo más usual.

Organización

La mayoría de módulos [DIM] se construyen usando "x4" (de 4) los chips de memoria o "x8" (de 8) con 9 chips de memoria de chips por lado. "X4" o "x8" se refieren a la anchura de datos de los chips DRAM en bits.

En el caso de los [DIMM] "x4", la anchura de datos por lado es de 36 bits, por lo tanto, el controlador de memoria (que requiere 72 bits) para hacer frente a las necesidades de ambas partes al mismo tiempo para leer y escribir los datos que necesita. En este caso, el módulo de doble cara es único en la clasificación.

Para "DIMM x8",cada lado es de 72 bits de ancho, por lo que el controlador de memoria sólo se refiere a un lado a la vez (el módulo de dos caras es de doble clasificación).

"Filas" de los módulos

Las filas no pueden ser accedidas simultáneamente como si compartieran el mismo camino de datos. El diseño físico de los chips [DRAM] en un módulo DIMM no hace referencia necesariamente al número de filas.

Las DIMMs frecuentemente son referenciadas como de "un lado" o de "doble lado", refiriéndose a la ubicación de los chips de memoria que están en uno o en ambos lados del chip DIMM. Estos términos pueden causar confusión ya que no se refieren necesariamente a cómo están organizados lógicamente los chips DIMM o a qué formas hay de acceder a ellos.

Por ejemplo, en un chip DIMM de una fila que tiene 64 bits de datos de entrada/salida, sólo hay conjunto de chips [DRAM] que se activan para leer o recibir una escritura en los 64 bits. En la mayoría de sistemas electronicos, los controladores de memoria son diseñados para acceder a todo el bus de datos del módulo de memoria.

En un chip DIMM de 64 bits hecho con dos filas, debe haber dos conjuntos de chips DRAM que puedan ser accedidos en tiempos diferentes. Sólo una de las filas puede ser accedida en un instante de tiempo desde que los bits de datos de los DRAM son enlazados para dos cargas en el DIMM.

Las filas son accedidas mediante señales "chip select" (CS). Por lo tanto para un módulo de dos filas, las dos [DRAM] con los bits de datos entrelazados pueden ser accedidas mediante una señal CS por [DRAM

SIMM

SIMM (siglas de Single In-line Memory Module), es un formato para módulos de memoria RAM que consisten en placas de circuito impreso sobre las que se montan los integrados de memoria DRAM. Estos módulos se inserta en zócalos sobre la placa base. Los contactos en ambas caras están interconectados, esta es la mayor diferencia respecto de sus sucesores los DIMMs. Fueron muy populares desde principios de los 80 hasta finales de los 90, el formato fue estandarizado por JEDEC bajo el número JESD-

PatillajesSIMM de 30 contactos

| Pin | Nombre | Descripción |

|---|---|---|

| 1 | VCC | +5 VDC |

| 2 | /CAS | Column Address Strobe |

| 3 | DQ0 | Data 0 |

| 4 | A0 | Address 0 |

| 5 | A1 | Address 1 |

| 6 | DQ1 | Data 1 |

| 7 | A2 | Address 2 |

| 8 | A3 | Address 3 |

| 9 | GND | Ground |

| 10 | DQ2 | Data 2 |

| 11 | A4 | Address 4 |

| 12 | A5 | Address 5 |

| 13 | DQ3 | Data 3 |

| 14 | A6 | Address 6 |

| 15 | A7 | Address 7 |

| 16 | DQ4 | Data 4 |

| 17 | A8 | Address 8 |

| 18 | A9 | Address 9 |

| 19 | A10 | Address 10 |

| 20 | DQ5 | Data 5 |

| 21 | /WE | Write Enable |

| 22 | GND | Ground |

| 23 | DQ6 | Data 6 |

| 24 | A11 | Address 11 |

| 25 | DQ7 | Data 7 |

| 26 | QP | Data Parity Out |

| 27 | /RAS | Row Address Strobe |

| 28 | /CASP | Column Address Strobe Parity |

| 29 | DP | Data Parity In |

| 30 | VCC | +5 VDC |

- QP y DP no está conectados en los modelos sin paridad

- A9 no está conectado en los de 256 kB.

- A10 no está conectado en los de 256 kB y 1 MB.

- A11 no está conectado en los de 256 kB, 1 MB y 4 MB. SIMM de 72 contactos

| Pin # | Non-Parity | Parity | Signal Description |

|---|---|---|---|

| 1 | VSS | VSS | Ground |

| 2 | DQ0 | DQ0 | Data 0 |

| 3 | DQ1 | DQ1 | Data 1 |

| 4 | DQ2 | DQ2 | Data 2 |

| 5 | DQ3 | DQ3 | Data 3 |

| 6 | DQ4 | DQ4 | Data 4 |

| 7 | DQ5 | DQ5 | Data 5 |

| 8 | DQ6 | DQ6 | Data 6 |

| 9 | DQ7 | DQ7 | Data 7 |

| 10 | VCC | VCC | +5 VDC |

| 11 | PD1 | PD1 | Presence Detect 1 |

| 12 | A0 | A0 | Address 0 |

| 13 | A1 | A1 | Address 1 |

| 14 | A2 | A2 | Address 2 |

| 15 | A3 | A3 | Address 3 |

| 16 | A4 | A4 | Address 4 |

| 17 | A5 | A5 | Address 5 |

| 18 | A6 | A6 | Address 6 |

| 19 | A10 | A10 | Address 10 |

| 20 | n/c | PQ8 | Data 8 (Parity 1) |

| 21 | DQ9 | DQ9 | Data 9 |

| 22 | DQ10 | DQ10 | Data 10 |

| 23 | DQ11 | DQ11 | Data 11 |

| 24 | DQ12 | DQ12 | Data 12 |

| 25 | DQ13 | DQ13 | Data 13 |

| 26 | DQ14 | DQ14 | Data 14 |

| 27 | DQ15 | DQ15 | Data 15 |

| 28 | A7 | A7 | Address 7 |

| 29 | A11 | A11 | Address 11 |

| 30 | VCC | VCC | +5 VDC |

| 31 | A8 | A8 | Address 8 |

| 32 | A9 | A9 | Address 9 |

| 33 | /RAS3 | RAS3 | Row Address Strobe 3 |

| 34 | /RAS2 | RAS2 | Row Address Strobe 2 |

| 35 | DQ16 | DQ16 | Data 16 |

| 36 | n/c | PQ17 | Data 17 (Parity 2) |

| 37 | DQ18 | DQ18 | Data 18 |

| 38 | DQ19 | DQ19 | Data 19 |

| 39 | VSS | VSS | Ground |

| 40 | /CAS0 | CAS0 | Column Address Strobe 0 |

| 41 | /CAS2 | CAS2 | Column Address Strobe 2 |

| 42 | /CAS3 | CAS3 | Column Address Strobe 3 |

| 43 | /CAS1 | CAS1 | Column Address Strobe 1 |

| 44 | /RAS0 | RAS0 | Row Address Strobe 0 |

| 45 | /RAS1 | RAS1 | Row Address Strobe 1 |

| 46 | A12 | A12 | Address 12 |

| 47 | /WE | WE | Read/Write |

| 48 | A13 | A13 | Address 13 |

| 49 | DQ20 | DQ20 | Data 20 |

| 50 | DQ21 | DQ21 | Data 21 |

| 51 | DQ22 | DQ22 | Data 22 |

| 52 | DQ23 | DQ23 | Data 23 |

| 53 | DQ24 | DQ24 | Data 24 |

| 54 | DQ25 | DQ25 | Data 25 |

| 55 | n/c | PQ26 | Data 26 (Parity 3) |

| 56 | DQ27 | DQ27 | Data 27 |

| 57 | DQ28 | DQ28 | Data 28 |

| 58 | DQ29 | DQ29 | Data 29 |

| 59 | DQ31 | DQ31 | Data 31 |

| 60 | DQ30 | DQ30 | Data 30 |

| 61 | VCC | VCC | +5 VDC |

| 62 | DQ32 | DQ32 | Data 32 |

| 63 | DQ33 | DQ33 | Data 33 |

| 64 | DQ34 | DQ34 | Data 34 |

| 65 | n/c | PQ35 | Data 35 (Parity 4) |

| 66 | PD2 | PD2 | Presence Detect 2 |

| 67 | PD3 | PD3 | Presence Detect 3 |

| 68 | PD4 | PD4 | Presence Detect 4 |

| 69 | PD5 | PD5 | Presence Detect 1 |

| 70 | PD6 | PD6 | Presence Detect 6 |

| 71 | PD7 | PD7 | Presence Detect 7 |

| 72 | VSS | VSS | Ground |

0 comentarios